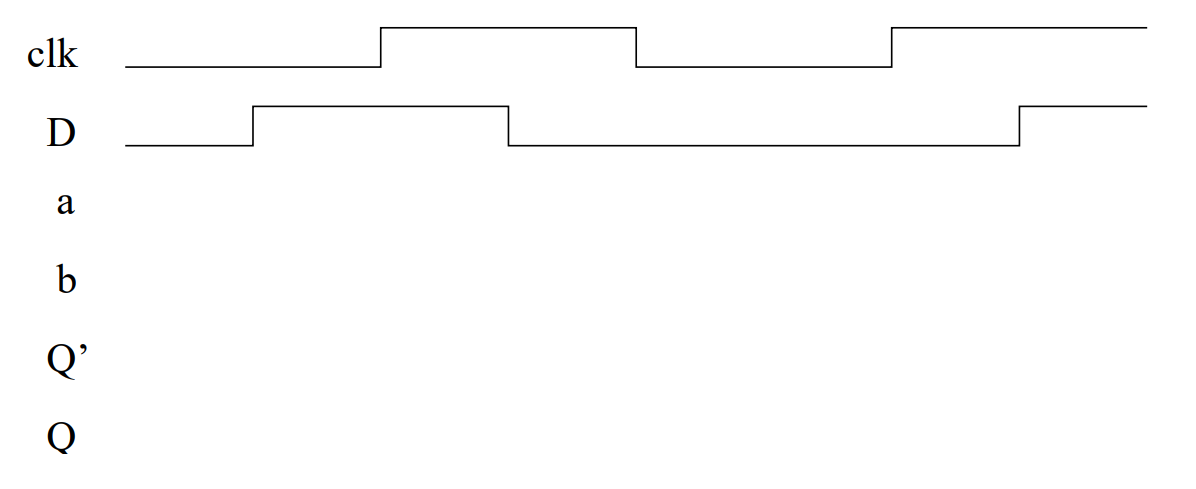

Figure 3 from A New Dynamic Floating Input D Flip-Flop (DFIDFF) for High Speed and Ultra Low Voltage Divided-by 4/5 Prescaler | Semantic Scholar

WO2017084217A1 - E-tspc structure-based low-power-consumption 2/3 frequency divider circuit - Google Patents

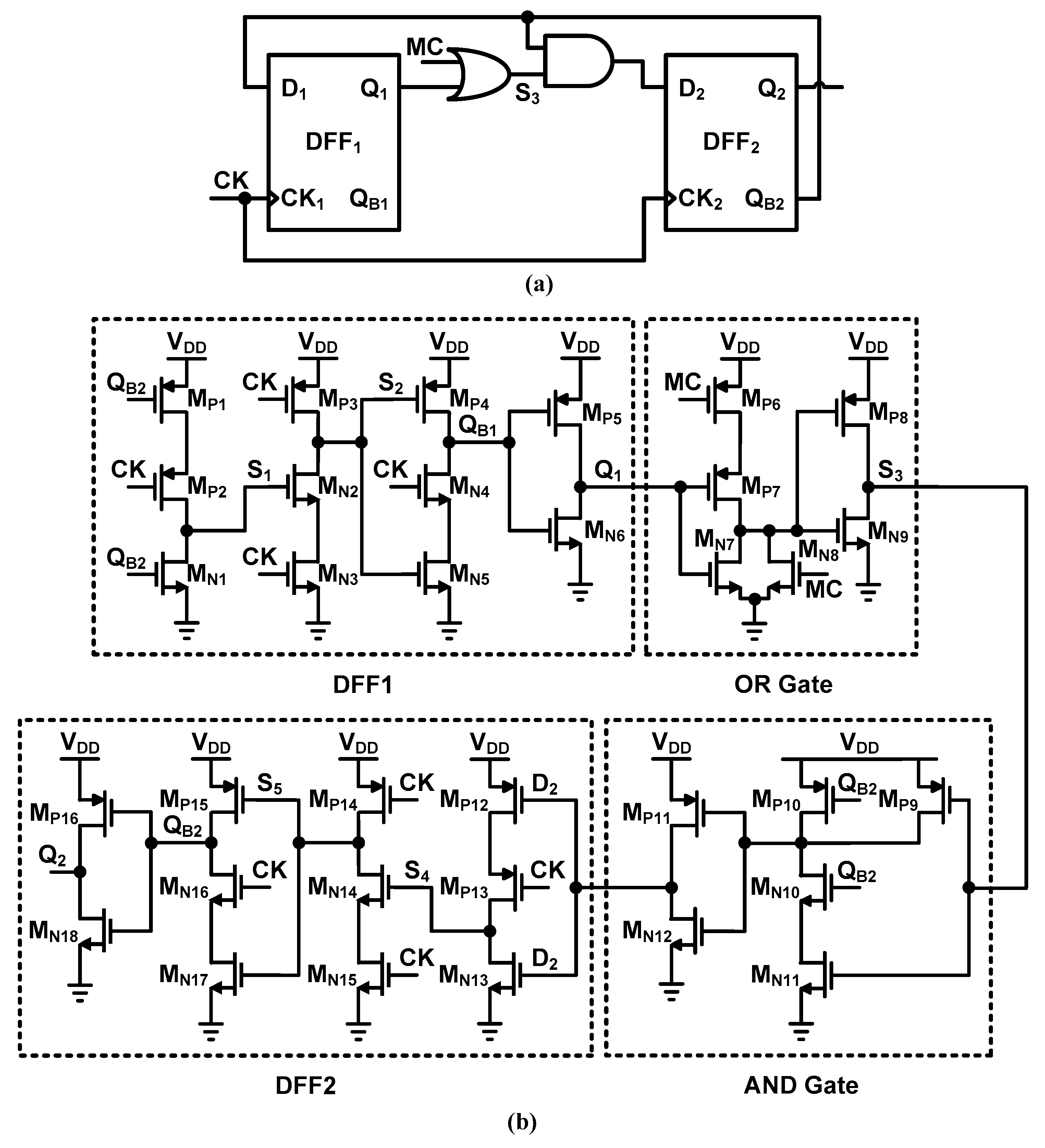

Electronics | Free Full-Text | High-Speed Wide-Range True-Single-Phase-Clock CMOS Dual Modulus Prescaler

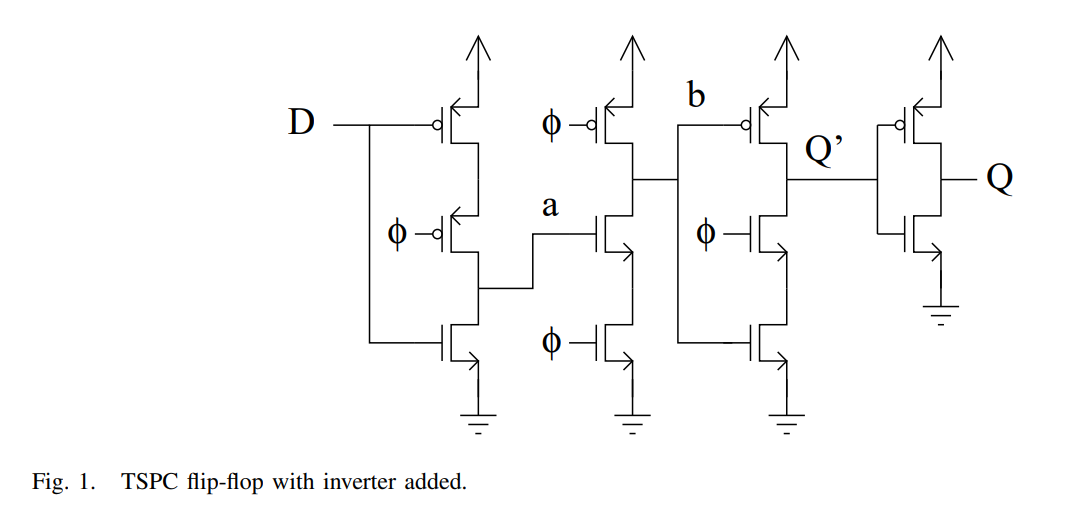

Configuration of TSPC D flip-flops (D-FF) for the asynchronous circuit.... | Download Scientific Diagram